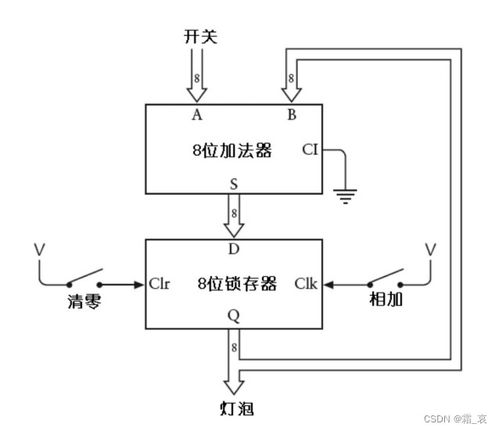

在《编码:隐匿在计算机软硬件背后的语言》第14章中,作者深入探讨了边沿触发器与计数器这两个构建现代计算机时序逻辑的核心组件。边沿触发器作为存储单元的基础,通过响应时钟信号的上升沿或下降沿来锁存数据,有效避免了电平触发器中常见的空翻现象。这种特性使其成为寄存器、内存等存储电路的理想选择。计数器的设计则展现了时序逻辑的巧妙应用——通过级联多个触发器并配置反馈逻辑,可实现二进制、十进制或任意进制的计数功能。从频率分频器到程序计数器,从时钟同步到状态机控制,这些基础模块共同构成了计算机协调运作的时序框架。本章通过电路图与波形分析的结合,揭示了数字系统中‘记忆’与‘时序’如何通过简单的逻辑门与触发器实现,为理解CPU流水线、缓存同步等高级概念奠定了实践基础。

边沿触发器与计数器 计算机时序逻辑的基石

更新时间:2026-04-19 23:25:20

如若转载,请注明出处:http://www.mingqi-gd.com/product/39.html

PRODUCT

产品列表